# uM-FPU64

# **64-bit Floating Point Coprocessor**

# **Instruction Set**

Release 411

# Introduction

The uM-FPU64 floating point coprocessor provides extensive support for 32-bit IEEE 754 compatible floating point and integer operations, 64-bit IEEE 754 compatible floating point and integer operations, and local peripheral device support.

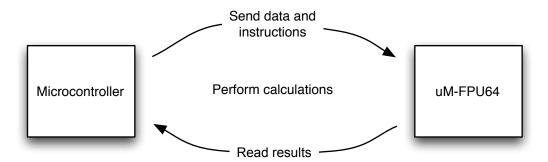

A typical calculation involves sending instructions and data from the microcontroller to the uM-FPU, performing the calculation, and transferring the result back to the microcontroller.

Instructions and data are sent to the uM-FPU using either a SPI or I<sup>2</sup>C interface. The uM-FPU64 chip has a 256 byte instruction buffer which allows for multiple instructions to sent. This improves the transfer times and allows the microcontroller to perform other tasks while the uM-FPU is performing a series of calculations. Prior to issuing any instruction that reads data from the uM-FPU, the Busy/Ready status must be checked to ensure that all instructions have been executed. If more than 256 bytes are required to specify a sequence of operations, the Busy/Ready status must be checked at least every 256 bytes to ensure that the instruction buffer does not overflow. See the datasheet for more detail regarding the SPI or I<sup>2</sup>C interfaces.

Instructions consist of an single opcode byte, optionally followed by addition data bytes. A detailed description of each instruction is provided later in this document, and a summary table is provided in Appendix A.

For instruction timing, see Appendix B of the uM-FPU64 Datasheet.

# uM-FPU Registers

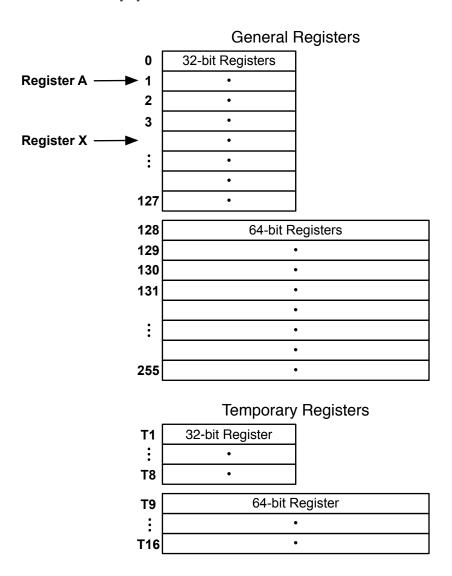

The uM-FPU64 has 256 general purpose registers, and 16 temporary registers. They can be used for storing floating point or integer values. The general purpose registers are numbered 0 to 255, and can be directly accessed by the instruction set. Registers 0 to 127 are 32-bit registers, and registers 128 to 255 are 64-bit registers. The 16 temporary registers are used by the **LEFT** and **RIGHT** instructions to store temporary results. They can be accessed through register A, but can't be accessed directly by the instruction set.

# Register A

All mathematical operations on the uM-FPU64 use a working register called register A. The value in register A is used as an operand for the mathematical operation, and the results of the operation are stored back to register A. Any general purpose registers can be selected as register A, using the **SELECTA** instruction. For example,

SELECTA, 5 register 5 is selected as register A

Register A also determines whether an operation is a 32-bit operation or a 64-bit operation. If register A is selected as register 0 to 127, the operation is 32-bit. If register A is selected as 128 to 255, the operation is 64-bit.

Arithmetic instructions that only involve one register implicitly refer to register A. For example, FNEG negate the value in register A

Arithmetic instructions that use two registers will specify the second register as part of the instruction. For example, FADD, 4 add the value of register 4 to register A

# Register X

Register X is used to reference a series of sequential registers. The register X selection is automatically incremented to the next register in sequence by all instructions that use register X. Any register can be selected as register X using the **SELECTX** instruction. For example,

SELECTX, 16

CLRX

CLRX

Clear register 16 (and increment register X)

CLRX

Clear register 17 (and increment register X)

CLRX

Clear register 18 (and increment register X)

Another example would be to use the FWRITEX and READX instructions to store and retrieve blocks of data.

# Register 0 and Register 128

Register 0 and register 128 are implicitly used by many instructions. Register 0 is used for 32-bit operations, and register 128 is used for 64-bit operations. They are used by many instructions to pass values or to return values.

Register 0 and register 128 can be used as general purpose registers, but since many instructions use these registers, they are normally only used to store temporary values. For example,

LOADPI load the value of pi to register 0 or 128 FSET0 store the value to register A

# **Register Abbreviations**

In this document the following abbreviations are used to refer to registers:

reg[0] register 0 (32-bit) reg[128] register 128 (64-bit)

reg[0 | 128] register 0 (32-bit) or register 128 (64-bit)

$\begin{array}{ll} \text{reg}[A] & \text{register A} \\ \text{reg}[X] & \text{register X} \end{array}$

reg[register]

any general purpose registers

reg[register1]

any general purpose registers

reg[register2]

any general purpose registers

# **Floating Point Instructions**

The following descriptions provide a quick summary of the floating point instructions. Detailed descriptions are provided in the next section.

# **Basic Floating Point Instructions**

Each of the basic floating point arithmetic instructions are provided in three different forms as shown in the table below. The **FADD** instruction is used as an example to describe the three different forms of these instructions. The **FADD**, **register** instruction allows any general purpose register to be added to register A. The register to be added to register A is specified by the byte following the opcode. The **FADDO** instruction adds register 0 to register A and only requires the opcode. The **FADDI** instruction adds a small integer value the register A. The signed byte (-128 to 127) following the opcode is converted to floating point and added to register A. The **FADD**, **register** instruction is most general, but the **FADDO** and **FADDI**, **signedByte** instructions are more efficient for many common operations.

| Register        | Register 0 | Immediate value    | Description      |

|-----------------|------------|--------------------|------------------|

| FSET, register  | FSET0      | FSETI, signedByte  | Set              |

| FADD,register   | FADD0      | FADDI, signedByte  | Add              |

| FSUB,register   | FSUB0      | FSUBI, signedByte  | Subtract         |

| FSUBR, register | FSUBR0     | FSUBRI, signedByte | Subtract Reverse |

| FMUL, register  | FMUL0      | FMULI, signedByte  | Multiply         |

| FDIV,register   | FDIV0      | FDIVI, signedByte  | Divide           |

| FDIVR, register | FDIVR0     | FDIVRI, signedByte | Divide Reverse   |

| FPOW,register   | FPOW0      | FPOWI, signedByte  | Power            |

| FCMP,register   | FCMP0      | FCMPI, signedByte  | Compare          |

# **Loading Floating Point Values**

The following instructions are used to load data from the microprocessor and store it on the uM-FPU64 as 32-bit floating point values. Register A determines whether 32-bit or 64-bit values are stored.

| FWRITE, register, float32Value   | Write 32-bit floating point value to register           |

|----------------------------------|---------------------------------------------------------|

| FWRITEO, float32Value            | Write 32-bit floating point value to reg[0] or reg[128] |

| FWRITEA, float32Value            | Write 32-bit floating point value to reg[A]             |

| FWRITEX, float32Value            | Write 32-bit floating point value to reg[X]             |

| DWRITE, register, float 64 Value | Write 64-bit floating point value to register           |

| ATOF, string                     | Convert ASCII string to floating point value and        |

|                                  | store in reg[0] or reg[128]                             |

| LOADBYTE, signedByte             | Convert signed byte to floating point and               |

|                                  | store in reg[0] or reg[128]                             |

| LOADUBYTE, unsignedByte          | Convert unsigned byte to floating point and             |

|                                  | store in reg[0] or reg[128]                             |

| LOADWORD, signedWord             | Convert signed 16-bit value to floating point and       |

|                                  | store in reg[0] or reg[128]                             |

| LOADUWORD, unsignedWord          | Convert unsigned 16-bit value to floating point and     |

|                                  | store in reg[0] or reg[128]                             |

| LOADE                            | Load the value of e (2.7182818) to reg[0] or reg[128]   |

| LOADPI                           | Load the value of pi (3.1415927) to reg[0] or reg[128]  |

| FCOPYI, unsignedByte, register   | Convert signed 8-bit value to floating point and        |

|                                  | store in register                                       |

### **Reading Floating Point Values**

The following instructions are used to read floating point values from the uM-FPU.

Return 32-bit floating point value from *register* FREAD, register [float32Value] FREADO [float32Value] Return 32-bit floating point value from reg[0] or reg[128] Return 32-bit floating point value from reg[A] FREADA [float32Value] FREADX [float32Value] Return 32-bit floating point value from reg[X] Return 64-bit floating point value from *register* DREAD, register [float64Value] Convert floating point to ASCII string FTOA, format (READSTR used to read string)

# **Additional Floating Point Instructions**

| FNEG           | SIN             | FSTATUS, register           | FLOOR |

|----------------|-----------------|-----------------------------|-------|

| FABS           | COS             | FSTATUSA                    | CEIL  |

| FINV           | TAN             | FCMP2, register1, register2 | ROUND |

| SQRT           | ASIN            | FMAC, register1, register2  | FRAC  |

| ROOT, register | ACOS            | FMSC, register1, register2  |       |

| LOG            | ATAN            | FCNV, conversion            |       |

| LOG10          | ATAN2, register | FMIN, register              |       |

| EXP            | DEGREES         | FMAX,register               |       |

| EXP10          | RADIANS         | FMOD                        |       |

#### **Matrix Instructions**

SELECTMA, register, rows, columns Select matrix A starting at register of size rows x columns SELECTMB, register, rows, columns Select matrix B starting at register of size rows x columns SELECTMC, register, rows, columns Select matrix C starting at register of size rows x columns Load reg[0] with value from matrix A row, column LOADMA, row, column Load reg[0] with value from matrix B row, column LOADMB, row, column Load reg[0] with value from matrix C row, column LOADMC, row, column Store reg[A] value to matrix A row, column SAVEMA, row, column Store reg[A] value to matrix A row, column SAVEMB, row, column Store reg[A] value to matrix A row, column SAVEMC, row, column Perform matrix operation MOP, action

#### **Fast Fourier Transform Instruction**

FFT, action Perform Fast Fourier Transform operation

#### Conversion Instructions

| FLOAT  | Convert reg[A] from long integer to floating point                 |

|--------|--------------------------------------------------------------------|

| FIX    | Convert reg[A] from floating point to long integer                 |

| FIXR   | Convert reg[A] from floating point to long integer (with rounding) |

| FSPLIT | Set reg[A] = integer value, reg[0] or reg[128] = fractional value  |

# **Long Integer Instructions**

The following descriptions provide a quick summary of the long integer instructions. Detailed descriptions are provided in the next section.

# **Basic Long Integer Instructions**

Each of the basic long integer arithmetic instructions are provided in three different forms as shown in the table below. The **LADD** instruction will be used as an example to describe the three different forms of the instructions. The **LADD**, **register** instruction allows any general purpose register to be added to register A. The register to be added to register A is specified by the byte following the opcode. The **LADDO** instruction adds register 0 to register A and only requires the opcode. The **LADDI** instruction adds a small integer value the register A. The signed byte (-128 to 127) following the opcode is converted to a long integer and added to register A. The **LADD**, **register** instruction is most general, but the **LADDO** and **LADDI**, **signedByte** instructions are more efficient for many common operations.

| Register        | Register 0 | Immediate value     | Description             |

|-----------------|------------|---------------------|-------------------------|

| LSET, register  | LSET0      | LSETI, signedByte   | Set                     |

| LADD, register  | LADD0      | LADDI, signedByte   | Add                     |

| LSUB,register   | LSUB0      | LSUBI,signedByte    | Subtract                |

| LMUL, register  | LMUL0      | LMULI, signedByte   | Multiply                |

| LDIV, register  | LDIV0      | LDIVI, signedByte   | Divide                  |

| LCMP, register  | LCMP0      | LCMPI, signedByte   | Compare                 |

| LUDIV, register | LUDIV0     | LUDIVI,unsignedByte | Unsigned Divide         |

| LUCMP, register | LUCMP0     | LUCMPI,unsignedByte | <b>Unsigned Compare</b> |

| LTST, register  | LTST0      | LTSTI,unsignedByte  | Test Bits               |

# **Loading Long Integer Values**

The following instructions are used to load data from the microprocessor and store it on the uM-FPU as 32-bit long integer values.

| LWRITE, register, int 32 Value | Write 32-bit long integer value to register           |

|--------------------------------|-------------------------------------------------------|

| LWRITE0, int32Value            | Write 32-bit long integer value to reg[0] or reg[128] |

| LWRITEA, int32Value            | Write 32-bit long integer value to reg[A]             |

| LWRITEX, int32Value            | Write 32-bit long integer value to reg[X]             |

| DWRITE, register, intValue     | Write 64-bit floating point value to register         |

| ATOL, string                   | Convert ASCII string to long integer value and        |

|                                | store in reg[0] or reg[128]                           |

| LONGBYTE, signedByte           | Convert signed byte to long integer and               |

|                                | store in reg[0] or reg[128]                           |

| LONGUBYTE, un signed Byte      | Convert unsigned byte to long integer and             |

|                                | store in reg[0] or reg[128]                           |

| LONGWORD, signedWord           | Convert signed 16-bit value to long integer           |

|                                | and store in reg[0] or reg[128]                       |

| LONGUWORD, un signed Byte      | Convert unsigned 16-bit value to long integer and     |

|                                | store in reg[0] or reg[128]                           |

| LCOPYI,unsignedByte,register   | Convert signed 8-bit value to long integer and        |

|                                | store in register                                     |

# **Reading Long Integer Values**

The following instructions are used to read long integer values from the uM-FPU.

Returns 32-bit long integer value from register LREAD, register [int32Value] LREADO [int32Value] Returns 32-bit long integer value from reg[0] or reg[128] Returns 32-bit long integer value from reg[A] LREADA [int32Value] Returns 32-bit long integer value from reg[X] LREADX [int32Value] Return 64-bit floating point value from register DREAD, register [int64Value] LREADBYTE [byteValue] Returns 8-bit byte from reg[A] Returns 16-bit value from reg[A] LREADWORD [wordValue] Convert long integer to ASCII string (use READSTR to LTOA, format read string)

# **Additional Long Integer Instructions**

| LSTATUS, register | LCMP2,register1,register2    | LAND, register     |

|-------------------|------------------------------|--------------------|

| LSTATUSA          | LUCMP2, register1, register2 | LANDI, unsignedByt |

|                   |                              | e                  |

| LNEG              | LMIN, register               | LOR, register      |

| LABS              | LMAX,register                | LORI,unsignedByte  |

| LNOT              | LSHIFT, register             | LXOR, register     |

| LINC, register    | LSHIFTI, signedByte          |                    |

| LDEC, register    | LBIT, unsignedByte, register |                    |

# **General Purpose Instructions**

| SELECTA, register | ALOADX                     | XSAVE, register | SETREAD  |

|-------------------|----------------------------|-----------------|----------|

| SELECTX, register | COPY,register1,register2   | XSAVEA          | SYNC     |

| CLR,register      | COPY0, register            | INDA            | VERSION  |

| CLRA              | COPYA, register            | INDX            | IEEEMODE |

| CLRX              | COPYX,register             | LEFT            | PICMODE  |

| CLR0              | SWAP, register1, register2 | RIGHT           | SETARGS  |

| LOAD,register     | SWAPA, register            | READVAR, item   | CHECKSUM |

| LOADA             | SETSTATUS, unsignedbyte    | RESET           | XOP      |

| LOADX             | READSTATUS                 | NOP             |          |

# **Special Purpose Instructions**

#### **Indirect Pointer Instructions**

SETIND, type, {register | address} Set indirect pointer

ADDIND, register, unsignedByte Add to indirect pointer

COPYIND, fromPtr, toPtr, countReg Copy using indirect pointers

LOADIND, register

SAVEIND, register

Load reg[0 | 128] using indirect pointer

Save reg[A] using indirect pointer

RDIND, type, count [dataValue1...dataValueN]

Read multiple data values from indirect pointer

WRIND, type, count, dataValue1...dataValueN

Write multiple data values to indirect pointer

### **Stored Function Instructions**

FCALL, function Call user-defined function stored in Flash

RET Return from user-defined function

RET, conditionCode

BRA, relativeOffset

BRA, conditionCode, relativeOffset

JMP, absoluteOffset

JMP, conditionCode, absoluteOffset

Conditional return from user-defined function

Unconditional branch inside user-defined function

Unconditional jump inside user-defined function

Conditional jump inside user-defined function

GOTO, register Computed goto

TABLE, tableSize, tableItem1...tableItemN

Table lookup

FTABLE, conditionCode, tableSize, tableItem1...tableItemN

Floating point reverse table lookup

LTABLE, conditionCode, tableSize, tableItem1...tableItemN

Long integer reverse table lookup

POLY, count, floatValue1...floatValueN

N<sup>th</sup> order polynomial

#### **Background Event Processing**

EVENT, action {, function} Background event processing

# **Analog to Digital Conversion Instructions**

ADCMODE, mode Select A/D trigger mode

ADCTRIG Manual A/D trigger

ADCSCALE, channel Set A/D floating point scale factor

ADCLONG, channel Get raw long integer A/D reading

ADCLOAD, channel Get scaled floating point A/D reading

ADCWAIT Wait for A/D conversion to complete

# **Digital I/O Instructions**

DIGIO, action{, mode} Digital I/O

DEVIO, device, action{,...} Device I/O

#### **Timer Instructions**

TIMESET Set timers

TIMELONG Get time in seconds

TICKLONG Get time in milliseconds

RTC, action Real-time Clock

DELAY, period Delay (in milliseconds)

# **External Input Instructions**

EXTSET Set external input counter

EXTLONG Get external input counter

EXTWAIT Wait for next external input pulse

### **String Manipulation Instructions**

STRSET, string

STRSEL, start, length

STRINS, string

STRBYTE

STRINC

STRDEC

STRCMP, string

Copy string to string buffer

Set string selection point

Insert string at selection point

Increment string selection point

Decrement string selection point

Compare string with string selection

STRFIND, string Find string

STRFCHR, string Set field delimiters

STRFIELD, field Find field

STRTOF Convert string selection to floating point

STRTOL Convert string selection to long integer

FTOA, format Convert floating point value to string

LTOA, format Convert long integer value to string

READSTR Read entire string buffer READSEL Read string selection

# **Serial Input/Output**

SEROUT, action { , ...} Serial Output

SERIN, action Serial Input

# **Debugging Instructions**

BREAK Debug breakpoint

TRACEOFF Turn debug trace off

TRACEON Turn debug trace on

TRACESTR, string Display string in debug trace

TRACEREG, register Display contents of register in debug trace

# **Test Conditions**

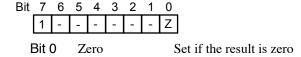

Several of the stored function instructions use a test condition byte. The test condition is an 8-bit byte that defines the expected state of the internal status byte. The upper nibble is used as a mask to determine which status bits to check. A status bit will only be checked if the corresponding mask bit is set to 1. The lower nibble specifies the expected value for each of the corresponding status bits in the internal status byte. A test condition is considered to be true if all of the masked test bits have the same value as the corresponding bits in the internal status byte. There are two special cases:  $0 \times 60$  evaluates as greater than or equal, and  $0 \times 62$  evaluates as less than or equal.

| Bit 7 6 5    | 4 3 2 1 0                             |

|--------------|---------------------------------------|

| Mask         | INSZ                                  |

| Bits 7:4 Ma  | sk bits                               |

| Bit 7        | Mask bit for Infinity                 |

| Bit 6        | Mask bit for NaN                      |

| Bit 5        | Mask bit for Sign                     |

| Bit 4        | Mask bit for Zero                     |

| Bits 3:0 Tes | st bits                               |

| Bit 3        | Expected state of Infinity status bit |

| Bit 2        | Expected state of NaN status bit      |

| Bit 1        | Expected state of Sign status bit     |

| Bit 0        | Expected state of Zero status bit     |

The uM-FPU V3 IDE assembler has built-in symbols for the most common test conditions. They are as follows:

| Assembler Symbol | Test Condition | Description           |

|------------------|----------------|-----------------------|

| Z                | 0x51           | Zero                  |

| EQ               | 0x51           | Equal                 |

| NZ               | 0x50           | Not Zero              |

| NE               | 0x50           | Not Equal             |

| LT               | 0x72           | Less Than             |

| LE               | 0x62           | Less Than or Equal    |

| GT               | 0x70           | Greater Than          |

| GE               | 0x60           | Greater Than or Equal |

| PZ               | 0x71           | Positive Zero         |

| MZ               | 0x73           | Negative Zero         |

| INF              | 0xC8           | Infinity              |

| FIN              | 0xC0           | Finite                |

| PINF             | 0xE8           | Positive Infinity     |

| MINF             | 0xEA           | Minus infinity        |

| NAN              | 0x44           | Not-a-Number (NaN)    |

| TRUE             | 0x00           | True                  |

| FALSE            | 0xFF           | False                 |

# uM-FPU64 Instruction Reference

ACOS Arc Cosine

Syntax: ACOS

Description: Calculates the arc cosine of an angle in the range 0.0 through pi. The initial value is contained in

register A, and the result is stored in register A.

reg[A] = acos(reg[A])

Opcode: 4B

Special Cases: • if reg[A] is NaN or its absolute value is greater than 1, then the result is NaN

See Also: ASIN, ATAN, ATAN2, COS, SIN, TAN, DEGREES, RADIANS

# ADCLOAD Load scaled analog value

Syntax: ADCLOAD, channel

Description: Loads register 0 with the scaled floating point value of the analog reading from the specified

channel.

if reg[A] is 32-bit,

reg[0] = (float(ADCvalue[channel]) \* ADCscale[channel])) + ADCoffset[channel]

if reg[A] is 64-bit,

reg[128] = (float(ADCvalue[channel]) \* ADCscale[channel])) + ADCoffset[channel]

Opcode: D5

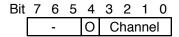

#### Byte 2: channel

| Bit | 7 | 6 | 5       | 4 | 3 | 2  | 1 | 0 |

|-----|---|---|---------|---|---|----|---|---|

|     | - |   | Channel |   |   | el |   |   |

| Bits 3:0 | Channel |                          |

|----------|---------|--------------------------|

|          | Value   | Description              |

|          | 0 to 5  | 28-pin chip (AN0 to AN5) |

|          | 0 to 8  | 44-pin chip (AN0 to AN8) |

Waits until the analog-to-digital conversion is complete, then loads register 0 with the reading from the specified analog channel. The 12-bit value is converted to floating point, multiplied by the scale value for the selected channel, and added to the offset for the selected channel. The value is stored in register 0.

Note: The instruction buffer should be empty when this instruction is executed. If there are other instructions in the instruction buffer, or another instruction is sent before the ADCLOAD instruction has been completed, the wait will terminate and the previous value for the selected channel will be

used.

See Also: ADCLONG, ADCMODE, ADCSCALE, ADCTRIG, ADCWAIT

# ADCLONG Load raw analog value

Syntax: ADCLONG, channel

Description: Loads register 0 with the long integer value of the raw analog reading from the specified channel,

or a pointer to the memory buffer containing the analog readings (if the PTR bit is set).

if reg[A] is 32-bit, reg[0] = ADCvalue[channel], status = longStatus(reg[0]) if reg[A] is 64-bit, reg[128] = ADCvalue[channel], status = longStatus(reg[128])

Opcode: D4

#### Byte 2: channel

| Bit | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0  |

|-----|---|---|---|---|---|-----|-----|----|

|     | - |   | S | Р | С | hai | nne | el |

| Bit 5    | Size<br>IDE Symbol<br>-<br>SIZE | IDE Value<br>0x00<br>0x20                         | Description Stores the analog reading in register 0. Stores the size of the memory buffer in register 0. Used in block mode. |

|----------|---------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Bit 4    | Pointer IDE Symbol - PTR        | IDE Value<br>0x00<br>0x10                         | Description Stores the analog reading in register 0. Stores a pointer to the memory buffer register 0. Used in block mode.   |

| Bits 3:0 | Channel Value 0 to 5 0 to 8     | Description<br>28-pin chip (Al<br>44-pin chip (Al | N0 to AN5)                                                                                                                   |

Waits until the analog-to-digital conversion is complete, then loads register 0 with the selected value. If bit 4 is zero, the 12-bit value reading from the specified analog channel is converted to a long integer and stored in register 0. If bit 4 is one, a pointer to the memory buffer containing the analog reading is stored in register 0. The memory buffer stores the 12-bit analog reading in sequential 16-bit words. The pointer option is normally used only when the ADC is configured for block mode sampling.

Note: The instruction buffer should be empty when this instruction is executed. If there are other instructions in the instruction buffer, or another instruction is sent before the ADCLONG instruction has been completed, the wait will terminate and the previous value for the selected channel will be returned.

See Also: ADCLOAD, ADCMODE, ADCSCALE, ADCTRIG, ADCWAIT

# ADCMODE Set ADC trigger mode

Syntax: ADCMODE, mode

Description: Set the trigger mode of the A/D converter. The mode is interpreted as follows:

Opcode: D1

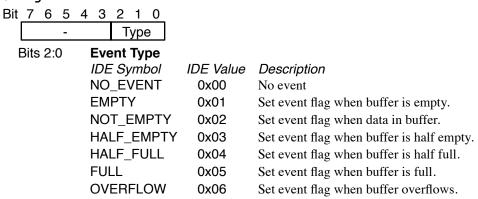

#### Byte 2: mode

| Bit 7 6 5 | 4 3 2 1 0  |           |                                |

|-----------|------------|-----------|--------------------------------|

| Action    | Options    |           |                                |

| Bits 7:4  | Action     |           |                                |

|           | IDE Symbol | IDE Value | Description                    |

|           | DISABLE    | 0x00      | Disable analog conversions     |

|           | MANUAL     | 0x10      | Manual trigger                 |

|           | EXTIN      | 0x20      | External trigger               |

|           | TIMER      | 0x30      | Timer trigger                  |

|           | EXTIN_BLK  | 0x40      | External trigger, block mode   |

|           | TIMER_BLK  | 0x50      | Timer trigger, block mode      |

|           | CHANNELS   | 0x60      | Maximum number of ADC channels |

|           | VREF       | 0x70      | Select voltage reference       |

Bits 3:0 **Options**

See descriptions below.

#### **DISABLE**

ADCMODE, DISABLE Disable analog conversions.

#### **MANUAL**

ADCMODE, MANUAL+repeat

Manual trigger, single sample with repeat.

#### **EXTIN**

ADCMODE, EXTIN+repeat

External trigger, single sample with repeat.

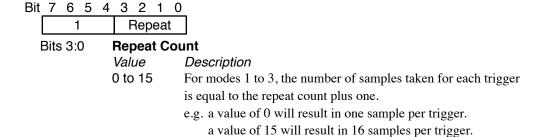

Bit 7 6 5 4 3 2 1 0

2 Repeat

Bits 3:0 Repeat Count

Value Description

0 to 15 For modes 1 to 3, the number of samples taken for each trigger

is equal to the repeat count plus one.

e.g. a value of  $\boldsymbol{0}$  will result in one sample per trigger.

a value of 15 will result in 16 samples per trigger.

#### **TIMER**

ADCMODE, TIMER+repeat

Timer trigger, single sample with repeat.

| Bit | 7 | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|-----|---|---|---|---|---|-----|----|---|

|     | 3 |   |   |   | F | Зер | ea | t |

Bits 3:0 Repeat Count

Value Description

0 to 15 For modes 1 to 3, the number of samples taken for each

trigger is equal to the repeat count plus one.

e.g. a value of 0 will result in one sample per trigger. a value of 15 will result in 16 samples per trigger.

The value in register 0 specifies the time interval in microseconds. The minimum time interval is 100 microseconds and the maximum time interval is 4294.967 seconds. Short time intervals (from 100 microseconds to 2 milliseconds) are accurate to the microsecond, whereas longer time intervals (greater than 2 milliseconds) are accurate to the millisecond.

### EXTIN\_BLK

ADCMODE, EXTIN\_BLK

External trigger, block mode with continuous sampling.

#### TIMER\_BLK

ADCMODE, TIMER\_BLK

Timer trigger, block mode with continuous sampling.

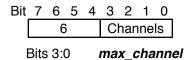

#### **CHANNELS**

ADCMODE, CHANNELS, max\_channel

Sets the maximum number of ADC channels.

Value Description

0 to 5 28-pin chip (AN0 to AN5) 0 to 8 44-pin chip (AN0 to AN8)

Sets the total number of analog channels to convert. The value specified is the maximum channel number. e.g. A value of 2 will convert ANO, AN1, AN2.

#### **VREF**

ADCMODE, VREF, vref\_bits Selects voltage reference.

| Bit   | 7 | 6 | 5 | 4   | 3 | 2 | 1  | 0  |

|-------|---|---|---|-----|---|---|----|----|

|       |   | 7 | 7 |     |   |   | V- | V+ |

| D:: 4 |   |   |   | ·/D |   |   |    |    |

Bit 1 **VREF-**

IDE SymbolIDE ValueDescriptionAVSS0x00AVSS is used as VREF-AN10x02AN1 is used as VREF-

Bit 0 VREF+

IDE Symbol IDE Value Description

AVDD ox00 AVDD is used as VREF+ ANO ANO is used as VREF+

Examples: ADCMODE, 0x10 Set manual trigger, single sample with one repeat per trigger.

ADCMODE, 0x24 Set external trigger, single sample with five samples per trigger.

LOADWORD, 1000 Set timer trigger every 1000 usec.

ADCMODE, 0x30 Single sample with one repeat per trigger.

ADCMODE, 0 Disable analog conversions.

See Also: ADCLOAD, ADCLONG, ADCSCALE, ADCTRIG, ADCWAIT

### ADCSCALE Set scale multiplier for ADC

Syntax: ADCSCALE, channel

Description: Set the scale value or offset value for the specified channel to the floating point value in register 0.

if reg[A] is 32-bit,

ADCscale[channel] = reg[0] or ADCoffset[channel] = reg[0]

if reg[A] is 64-bit,

ADCscale[channel] = reg[128] or ADCoffset[channel] = reg[128]

Opcode: D3

Byte 2: channel

Bit 4 Scale/Offset

IDE SymbolIDE ValueDescription-0x00Sets scale value.OFFSET0x10Sets offset value.

Bits 3:0 Channel

Value Description

0 to 5 28-pin chip (AN0 to AN5) 0 to 8 44-pin chip (AN0 to AN8)

Sets the scale value or offset value for *channel* to the floating point value in register 0. At device reset, the scale value for all channels is set to 1.0, and the offset value for all channels is set to zero.

See Also: ADCLOAD, ADCLONG, ADCMODE, ADCTRIG, ADCWAIT

# ADCTRIG Trigger an A/D conversion

Syntax: ADCTRIG

Description: Trigger an analog conversion. If a conversion is already in progress the trigger is ignored. This is

normally used only when the ADCMODE is set for manual trigger.

Opcode: D2

See Also: ADCLOAD, ADCLONG, ADCMODE, ADCSCALE, ADCWAIT

## ADCWAIT Wait for next A/D sample

Syntax: ADCWAIT

Description: Wait until the next analog conversion is complete and the analog values are ready.

Opcode: D6

When ADCMODE is set for manual trigger, this instruction can be used to wait until the conversion started by the last ADCTRIG is done. ADCLONG and ADCLOAD automatically wait until the next sample is ready. If the ADCMODE is set for timer trigger or external input trigger, this instruction will wait until the next full conversion is completed.

Note: The instruction buffer should be empty when this instruction is executed. If there are other instructions in the instruction buffer, or another instruction is sent before the ADCWAIT instruction has been completed, the wait will terminate.

See Also: ADCLOAD, ADCLONG, ADCMODE, ADCSCALE, ADCTRIG

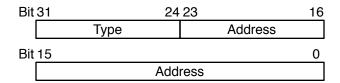

#### ADDIND Add to Indirect Pointer

Syntax: ADDIND, register, unsignedByte

Description: The long integer value in register is multiplied by the unsignedByte and by the data type size and

the result is added to bits 23:0 of register 0 or 128 (pointer address). Bits 31:24 of register 0 or 128

are unchanged (pointer type). See the SETIND instruction for a description of pointers.

if reg[A] is 32-bit,

reg[0] (bits 31:24) = reg[0] (bits 31:24)

reg[0] (bits 23:0) = (reg[0] (bits23:0) + (reg[register] \* unsignedByte \* dataTypeSize

if reg[A] is 64-bit,

reg[128] (bits 63:32) = 0

reg[128] (bits 31:24) = reg128 (bits 63:24)

reg[128] (bits 23:0) = (reg[128] (bits23:0) + (reg[register] \* unsignedByte \*

dataTypeSize

*Opcode:* **78**

Byte 2: register

Register number (0 to 255).

Byte 3: unsigned

Unsigned byte (0 to 255).

Special Cases: • if register = 0, the register value is not used in the pointer calculation

• if register = 0 and unsigned Byte = 0, the pointer is decremented by the data type size

• if result is < 0, reg[0|128] (bits 23:0) is set to 0

• if result is >= 0xFFFFFF, reg[0l128] (bits 23:0) is set to 0xFFFFFF

See Also: SETIND, WRIND, RDIND, COPYIND, LOADIND, SAVEIND

# ALOADX Load register A from register X

Syntax: ALOADX

Description: Set register A to the value of register X, and increment X to select the next register in sequence.

reg[A] = reg[X], X = X + 1

Opcode: **OD**

Special Cases: • if reg[A] is 32-bit and reg[X] is 64-bit, only the lower 32-bits of reg[X] are copied

• if reg[A] is 64-bit and reg[X] is 32-bit, the upper 32-bits of reg[A] are set to zero

See Also: LOAD, LOADA, LOADX, XSAVE, XSAVEA

ASIN **Arc Sine**

Syntax: ASIN

Description: Calculates the arc sine of an angle in the range of -pi/2 through pi/2. The initial value is contained

in register A, and the result in stored in register A.

reg[A] = asin(reg[A])

Opcode: 4A

• if reg[A] is NaN or its absolute value is greater than 1, then the result is NaN Special Cases:

> • if reg[A] is 0.0, then the result is a 0.0 • if reg[A] is -0.0, then the result is -0.0

See Also: ACOS, ATAN, ATAN2, COS, SIN, TAN, DEGREES, RADIANS

**ATAN** Arc Tangent

Syntax: **ATAN**

Description: Calculates the arc tangent of an angle in the range of -pi/2 through pi/2. The initial value is

contained in register A, and the result in stored in register A.

reg[A] = atan(reg[A])

Opcode: 4C

Special Cases: • if reg[A] is NaN, then the result is NaN

> • if reg[A] is 0.0, then the result is a 0.0 • if reg[A] is -0.0, then the result is -0.0

See Also: ACOS, ASIN, ATAN2, COS, SIN, TAN, DEGREES, RADIANS

ATAN2 **Arc Tangent (with two registers)**

Syntax: ATAN2, register

Description: Calculates the arc tangent of an angle in the range of -pi/2 through pi/2. The initial value is

> determined by dividing the value in register A by the value of the specified register, and the result in stored in register A. This instruction is used to convert rectangular coordinates (register A, reg[register]) to polar coordinates (r, theta). The value of theta is stored in register A.

reg[A] = atan(reg[A] / reg[register])

Opcode: **4D**

*Byte 2:* register Register number (0 to 255).

#### Special Cases:

- if reg[A] is 32-bit and *register* is 64-bit, the value from *register* is converted to a 32-bit value before being used, but the value stored in *register* remains unchanged

- if reg[A] is 64-bit and *register* is 32-bit, the value in *register* is converted to a 64-bit value before being used, but value stored in *register* remains unchanged

- if reg[A] or reg[register] is NaN, then the result is NaN

- if reg[A] is 0.0 and reg[register] > 0, then the result is 0.0

- if reg[A] > 0 and finite, and reg[register] is +inf, then the result is 0.0

- if reg[A] is -0.0 and reg[register] > 0, then the result is -0.0

- if reg[A] < 0 and finite, and reg[register] is +inf, then the result is -0.0

- if reg[A] is 0.0 and reg[register] < 0, then the result is pi

- if reg[A] > 0 and finite, and reg[register] is -inf, then the result is pi

- if reg[A] is -0.0, and reg[register] < 0, then the result is -pi

- if reg[A] < 0 and finite, and reg[register] is -inf, then the result is -pi

- if reg[A] > 0, and reg[register] is 0.0 or -0.0, then the result is pi/2

- if reg[A] is +inf, and reg[register] is finite, then the result is pi/2

- if reg[A] < 0, and reg[register] is 0.0 or -0.0, then the result is -pi/2

- if reg[A] is -inf, and reg[register] is finite, then the result is -pi/2

- if reg[A] is +inf, and reg[register] is +inf, then the result is pi/4

- if reg[A] is +inf, and reg[register] is -inf, then the result is 3\*pi/4

- if reg[A] is -inf, and reg[register] is +inf, then the result is -pi/4

- if reg[A] is -inf, and reg[register] is -inf, then the result is -3\*pi/4

See Also: ACOS, ASIN, ATAN, COS, SIN, TAN, DEGREES, RADIANS

# ATOF Convert ASCII string to floating point

Syntax: ATOF, string

Description: Converts a zero terminated ASCII string to a floating point value. and stores the result in register 0

or register 128.

Opcode: 1E

Byte 2: string

Zero-terminated ASCII string.

If register A is 32-bit, register 0 is loaded with the 32-bit floating point value. If register A is 64-bit, register 128 is loaded with the 64-bit floating point value. The *string* to convert is sent immediately following the opcode. The string can be in standard numeric format (e.g. 1.56, -0.5), or exponential format (e.g. 10E6). Conversion will stop at the first invalid character, but data bytes will continue to be read until a zero terminator is encountered. The *string* can contain the following characters:

- leading whitespace (space or tab)

- sign (+ or -)

- decimal digits (0 to 9)

- decimal point (.)

- decimal digits (0 to 9)

- exponential (E or e)

• sign (+ or -)

• decimal digits (0 to 9)

Examples: ATOF, "2.54" stores the value 2.54 in register 0 or 128

ATOF, "1E3" stores the value 1000.0 in register 0 or 128

Special Cases: • if string length > 127, string will be truncated to 127 characters

See Also: ATOL, FTOA, LTOA, STRTOF, STRTOL

# ATOL Convert ASCII string to long integer

Syntax: ATOL, string

Description: Converts a zero terminated ASCII string to a long integer value.

Opcode: 9A

Byte 2: string

Zero-terminated ASCII string.

If register A is 32-bit, register 0 is loaded with the 32-bit long integer value. If register A is 64-bit, register 128 is loaded with the 64-bit long integer value. The *string* to convert is sent immediately following the opcode. Conversion will stop at the first invalid character, but data bytes will continue to be read until a zero terminator is encountered. The *string* can contain the following characters:

• leading whitespace (space or tab)

• sign (+ or -)

• decimal digits (0 to 9)

Examples: ATOL, "500000" stores the value 500000 in register 0 or 128

ATOL, "-5" stores the value -5 in register 0 or 128

Special Cases: • if string length > 127, string will be truncated to 127 characters

See Also: ATOF, FTOA, LTOA, STRTOF, STRTOL

#### BRA Unconditional branch

Syntax: BRA, relativeAddress

Description: This instruction branches unconditionally to the instruction at the relative Address. If the

relativeAddress is more than -128 to 127 bytes from the address of the next instruction, the JMP

instruction must be used.

Opcode: 81

Byte 2: relativeAddress

A signed byte value that is added to the address of the next instruction to determine the address to

branch to.

Special Cases: • only valid inside user-defined functions stored in Flash memory.

See Also: BRA, cc, JMP, JMP, cc, GOTO, RET, RET, cc

## BRA, cc Conditional branch

Syntax: BRA, conditionCode, relativeAddress

Description: If the condition is true, this instruction branches to the instruction at the relativeAddress address. If

the condition is false, no branch occurs. If the relative Address is more than -128 to 127 bytes from

the address of the next instruction, the JMP, cc instruction must be used.

*Opcode:* **82**

#### Byte 2: conditionCode

The list of condition codes is as follows:

| IDE Symbol   | IDE Value | Description           |

|--------------|-----------|-----------------------|

| $\mathbf{z}$ | 0x51      | Zero                  |

| EQ           | 0x51      | Equal                 |

| NZ           | 0x50      | Not Zero              |

| NE           | 0x50      | Not Equal             |

| LT           | 0x72      | Less Than             |

| LE           | 0x62      | Less Than or Equal    |

| GT           | 0x70      | Greater Than          |

| GE           | 0x60      | Greater Than or Equal |

| PZ           | 0x71      | Positive Zero         |

| MZ           | 0x73      | Negative Zero         |

| INF          | 0xC8      | Infinity              |

| FIN          | 0xC0      | Finite                |

| PINF         | 0xE8      | Positive Infinity     |

| MINF         | 0xEA      | Minus infinity        |

| NAN          | 0x44      | Not-a-Number (NaN)    |

| TRUE         | 0x00      | True                  |

| FALSE        | 0xFF      | False                 |

### Byte 3: relativeAddress

A signed byte value that is added to the address of the next instruction to determine the address to branch to.

Special Cases: • only valid inside user-defined functions stored in Flash memory.

See Also: BRA, JMP, JMP, cc, GOTO, RET, RET, cc

# **BREAK** Debug breakpoint

Syntax: BREAK

Description: If debug mode is enabled, a breakpoint occurs and the debug monitor is entered. If debug mode is

disabled, the instruction is ignored.

Opcode: F7

Used in conjunction with the built-in debugger.

See Also: TRACEOFF, TRACEON, TRACEREG, TRACESTR

# CEIL Ceiling

Syntax: CEIL

Description: Calculates the floating point value equal to the nearest integer that is greater than or equal to the

floating point value in register A. The result is stored in register A.

reg[A] = ceil(reg[A])

*Opcode:* **52**

Special Cases: • if is NaN, then the result is NaN

• if reg[A] is +infinity or -infinity, then the result is +infinity or -infinity

• if reg[A] is 0.0 or -0.0, then the result is 0.0 or -0.0

• if reg[A] is less than zero but greater than -1.0, then the result is -0.0

See Also: FLOOR, ROUND

### CHECKSUM Calculate checksum for uM-FPU code

Syntax: CHECKSUM

Description: A checksum is calculated for the uM-FPU64 code and user-defined functions stored in Flash. The

checksum value is stored in register 0.

Opcode: F6

This can be used as a diagnostic test for confirming the state of a uM-FPU chip.

# CLR Clear register

Syntax: CLR, register

Description: Set the value of the specified register to zero.

reg[register] = 0, status = longStatus(reg[register])

*Opcode:* **03**

Byte 2: register

Register number (0 to 255).

Special Cases: • if SETARGS is used, and register = 0

• if reg[A] is 32-bit, the value is stored in registers 1 to 9

• if reg[A] is 64-bit, the value is stored in registers 129 to 137

See Also: CLRO, CLRA, CLRX, SETARGS

# CLR0 Clear register 0

Syntax: CLRO

Description: Set the value of register 0 (32-bit) or register 128 (64-bit) to zero.

if reg[A] is 32-bit, reg[0] = 0, status = longStatus(reg[0]) if reg[A] is 64-bit, reg[128] = 0, status = longStatus(reg[128])

*Opcode:* **06**

Special Cases: • if SETARGS is used,

• if reg[A] is 32-bit, the value is stored in registers 1 to 9

• if reg[A] is 64-bit, the value is stored in registers 129 to 137

See Also: CLR, CLRA, CLRX, SETARGS

## CLRA Clear register A

Syntax: CLRA

Description: Set the value of register A to zero.

reg[A] = 0, status = longStatus(reg[A])

Opcode: 04

See Also: CLR, CLRO, CLRX

# CLRX Clear register X

Syntax: CLRX

Description: Set the value of register A to zero, and increment X to select the next register in sequence.

reg[X] = 0, status = longStatus(reg[X]), X = X + 1

*Opcode:* **05**

Special Cases: • if reg[X] is 32-bit, X will not be incremented past register 127

• if reg[X] is 64-bit, X will not be incremented past register 255

See Also: CLR, CLRO, CLRA

**COPY** Copy registers

Syntax: COPY, fromRegister, toRegister

Description: Copy the value from from Register to to Register.

reg[toRegister] = reg[fromRegister], status = longStatus(reg[toRegister])

*Opcode:* **07**

Byte 2: fromRegister

Register number (0 to 255).

Byte 3: toRegister

Register number (0 to 255).

Special Cases: • if to Register is 32-bit and from Register is 64-bit, the upper 32-bits of from Register are set to zero

• if toRegister is 64-bit and fromRegister is 32-bit, only the lower 32-bits of toRegister are copied

See Also: COPYA, COPYX, COPYO, FCOPYI, LCOPYI

COPYA Copy register A

Syntax: COPYA, register

Description: Copy the value of register A to register.

reg[register] = reg[A], status = longStatus(reg[A])

Opcode: 08

Byte 2: register

Register number (0 to 255).

Special Cases: • if reg[A] is 32-bit and register is 64-bit, the upper 32-bits of register are set to zero

• if reg[A] is 64-bit and register is 32-bit, only the lower 32-bits of reg[A] are copied

See Also: COPY, COPYX, COPYO, FCOPYI, LCOPYI

**COPYIND** Copy using Indirect Pointers

Syntax: COPYIND, from Register, to Register, count Register

Description: The number of data items specified by the countRegister are copied from the location pointed to

by from Register to the location pointed to by to Register. See the SETIND instruction for a

description of pointers.

*Opcode:* **79**

Byte 2: fromRegister

Register number (0 to 255). The register contains the from pointer.

Byte 3: toRegister

Register number (0 to 255). The register contains the to pointer.

Byte 4: countRegister

Register number (0 to 255). The register contains the number of items to copy.

See Also: SETIND, ADDIND, WRIND, RDIND, LOADIND, SAVEIND

# COPYX Copy register X

Syntax: COPYX, register

Description: Copy the value of register X to register, and increment X to select the next register in sequence.

reg[register] = reg[X], status = longStatus(reg[register]), X = X + 1

*Opcode:* **09**

Byte 2: register

Register number (0 to 255).

Special Cases: • if reg[X] is 32-bit and register is 64-bit, the upper 32-bits of register are set to zero

• if reg[X] is 64-bit and register is 32-bit, only the lower 32-bits of reg[X] are copied

See Also: COPY, COPYA, COPYO, FCOPYI, LCOPYI

## COPY0 Copy register 0

Syntax: COPYO, register

Description: If register A is 32-bit, the value of register 0 is copied to register.

If register A is 64-bit, the value of register 128 is copied to register.

if reg[A] is 32-bit, then reg[register] = reg[0], status = longStatus(reg[0]) if reg[A] is 64-bit, then reg[register] = reg[128], status = longStatus(reg[128])

*Opcode:* **10**

Byte 2: register

Register number (0 to 255).

Special Cases: • if reg[A] is 32-bit and register is 64-bit, the upper 32-bits of register are set to zero

• if reg[A] is 64-bit and register is 32-bit, only the lower 32-bits of reg[128] are copied

See Also: COPY, COPYA, COPYX, FCOPYI, LCOPYI

COS Cosine

Syntax: COS

Description: Calculates the cosine of the angle (in radians) in register A and stores the result in register A.

reg[A] = cosine(reg[A])

Opcode: 48

Special Cases: • if reg[A] is NaN or an infinity, then the result is NaN

See Also: ACOS, ASIN, ATAN, ATAN, SIN, TAN, DEGREES, RADIANS

**DEGREES** Convert radians to degrees

Syntax: DEGREES

Description: The floating point value in register A is converted from radians to degrees and the result is stored

in register A.

Opcode: 4E

Special Cases: • if reg[A] is NaN, then the result is NaN

See Also: ACOS, ASIN, ATAN, ATAN2, COS, SIN, TAN, RADIANS

**DELAY** Delay (in milliseconds)

Syntax: DELAY, period

Description: The uM-FPU64 pauses for the number of milliseconds specified by period. If period is zero, then

the number of milliseconds is loaded from register 0. If foreground/background processing has

been enabled, the other process can continue execution during the delay period.

Opcode: DB

Bytes 2-3: period

A 16-bit unsigned value that specified the delay period in milliseconds. (0 to 65535)

Special Cases: • the period is the minimum delay period, it can be up to one millisecond longer

See Also: TIMESET, TIMELONG, TICKLONG, RTC

**DEVIO** Device Input/Output

Syntax: DEVIO, device, action{,...}

Description:

This instruction provides support for devices interfaced to the uM-FPU64 chip using the digital pins. The DEVIO instruction is designed to interact with byte oriented I/O devices. It provides general I/O capabilities and higher level device specific support. All DEVIO instructions start with the opcode, followed by a byte that specifies the device, and a byte which specifies the action to perform with the device. Depending on the action, there may be additional bytes required by the instruction. The supported devices are: general access RAM, FIFO buffers, 1-wire bus, I²C bus, SPI bus, asynchronous serial port, counters, servo controllers, LCD, and VDrive2 USB Flash drives. Additional information is available in the *Using the uM-FPU64 DEVIO Instruction* document.

```

DEVIO, device, DISABLE

DEVIO, device, ENABLE, pin, config

DEVIO, device, {device specific actions}

DEVIO, device, WRITE_REG8{+MSB}{+LSB}, register

DEVIO, device, WRITE REG16{+MSB}{+LSB}, register

DEVIO, device, WRITE REG32{+MSB}+LSB}, register

DEVIO, device, WRITE REG64(+MSB)(+LSB), register

DEVIO, device, WRITE BYTE, byte

DEVIO, device, WRITE WORD, byte, byte

DEVIO, device, WRITE NBYTE, count, byte, ...

DEVIO, device, WRITE REP, count, byte

DEVIO, device, WRITE STR, string

DEVIO, device, WRITE SBUF

DEVIO, device, WRITE SSEL

DEVIO, device, WRITE MEM, count

DEVIO, device, WRITE MEMA, address, count

DEVIO, device, WRITE MEMR, regAddr, regCount

DEVIO, device, READ REG8{+MSB}{+LSB}{+ZE}{+SE}, register

DEVIO, device, READ REG16{+MSB}{+LSB}{+ZE}{+SE}, register

DEVIO, device, READ REG32{+MSB}{+LSB}{+ZE}{+SE}, register

DEVIO, device, READ REG64{+MSB}{+LSB}{+ZE}{+SE}, register

DEVIO, device, READ SKIP, count

DEVIO, device, READ SBUF

DEVIO, device, READ SSEL

DEVIO, device, READ MEM, count

DEVIO, device, READ MEMA, address, count

DEVIO, device, READ MEMR, regAddr, regCount

DEVIO, device, READ MEMR, regAddr, regCount

DEVIO, device, LOAD DEVICE, xopdev

```

#### Opcode: DA

## Byte 2: device

| Bit | 7    | 6   | 5 4 | 3   | 2 1   | 0    |    |       |      |        |          |

|-----|------|-----|-----|-----|-------|------|----|-------|------|--------|----------|

|     | D    | ev  | ice | N   | umb   | er   |    |       |      |        |          |

|     | Bits | 7:4 | ļ   | Dev | ice ' | Туре |    |       |      |        |          |

|     |      |     |     | IDE | Syn   | nbol | 1. | DE Va | alue | Devic  | е Туре   |

|     |      |     |     | ME  | EΜ    |      |    | 0x00  | )    | Memo   | ry       |

|     |      |     |     | F   | FO:   | L    |    | 0x01  |      | FIFO b | ouffer 1 |

|     |      |     |     | F   | FO    | 2    |    | 0x02  | )    | FIFO b | ouffer 2 |

| FIFO3           | 0x03 | FIFO buffer 3                 |

|-----------------|------|-------------------------------|

| FIFO4           | 0x04 | FIFO buffer 4                 |

| OWIRE           | 0x10 | 1-Wire                        |

| I2C             | 0x20 | I <sup>2</sup> C              |

| SPI             | 0x30 | SPI                           |

| ASYNC           | 0x40 | Asynchronous Serial Port      |

| COUNTER         | 0x50 | Counter (Digital input)       |

| SERVO           | 0x60 | Servo Output                  |

| LCD             | 0x80 | LCD                           |

| loadable device | 0xA0 | Reserved for loadable devices |

| loadable device | 0xB0 | Reserved for loadable devices |

| loadable device | 0xC0 | Reserved for loadable devices |

| loadable device | 0xD0 | Reserved for loadable devices |

| loadable device | 0xE0 | Reserved for loadable devices |

| loadable device | 0xF0 | Reserved for loadable devices |

#### Bits 3:0 Device Number

Value Description

0 - 15 Device number (for device types that support multiple devices)

#### Byte 3: action

An unsigned byte specifying the device action. A description of actions that are common to all devices is shown below. For device specific actions, see separate descriptions for each device type. (e.g. *DEVIO*, *ASYNC*)

#### Disable (0x00)

DEVIO, device, DISABLE

Disable the specified device and release the digital pins.

#### Enable (0x01)

DEVIO, device, ENABLE, pin, config

Enable the specified device and assign the digital pins. The enable instruction must be used to initialize a device before any other device instructions are used.

## Byte 4: pin

Specifies the first pin used by the specified device (D0 to D23).

#### Byte 5: config

Configuration byte for initializing the device. See the device specific descriptions for details.

#### **Device Specific Actions (0x02 - 0x0F)**

For device specific actions, see the separate documentation for each device type. (e.g. *DEVIO*, *ASYNC*)

#### Write 8-bit Value from Register (0x10, 0x14)

DEVIO, device, WRITE\_REG8, register

Write the lower 8-bit value from the specified register to the device.

#### Write 16-bit Value from Register (0x11, 0x15)

DEVIO, device, WRITE\_REG16{+MSB}{+LSB}, register

Write the lower 16-bit value from the specified register to the device. The value can be written with the most significant byte or least significant byte first.

### Write 32-bit Value from Register (0x12, 0x16)

DEVIO, device, WRITE REG32{+MSB}{+LSB}, register

Write the lower 32-bit word from the specified register to the device. The value can be written with the most significant byte or least significant byte first.

#### Write 64-bit Value from Register (0x13, 0x17)

DEVIO, device, WRITE\_REG64(+MSB)(+LSB), register

Write the 64-bit value from the specified register to the device. The value can be written with the most significant byte or least significant byte first.

| Bit 7 6 5 | 4 3 2 1 0<br>- L Bits           |                   |                                                          |

|-----------|---------------------------------|-------------------|----------------------------------------------------------|

| Bit 3     | Byte Order<br>IDE Symbol<br>MSB | IDE Value<br>0x00 | Description Most eignificant buts first                  |

|           | LSB                             | 0x00<br>0x04      | Most significant byte first Least significant byte first |

| Bits 1:0  | Number of Bi                    | ts                | 8 7                                                      |

|           | IDE Symbol                      | IDE Value         | Description                                              |

|           | WRITE_REG8                      | 0x10              | 1 byte (8-bit)                                           |

|           | WRITE_REG1                      | 6 0x11            | 2 bytes (16-bit)                                         |

|           | WRITE_REG3                      | 2 0x12            | 3 bytes (32-bit)                                         |

|           | WRITE_REG6                      | 64 0x13           | 4 bytes (64-bit)                                         |

## Byte 4: register

Register number (0 to 255).

#### Write Byte (0x20)

DEVIO, device, WRITE\_BYTE, byte Write the 8-bit value specified to the device.

#### Byte 4: byte

Unsigned 8-bit value to write to device.

## Write Word (0x21)

DEVIO, device, WRITE\_WORD, word

Write the 16-bit value specified to the device.

#### Bytes 4-5: word

Unsigned 16-bit value to write to device.

# Write Multiple Bytes (0x22)

DEVIO, device, WRITE\_NBYTE, count, byte, ... Write the number of bytes specified by count to the device.

#### Byte 4: count

Unsigned 8-bit integer specifying the number of bytes to write.

#### Bytes 5-n: byte, ...

Unsigned 8-bit values to write to device.

#### Write Repeat Byte (0x23)

DEVIO, device, WRITE\_REP, count, byte

Write the same byte repeatedly to the device the number of times specified by *count*.

#### Byte 4: count

Unsigned 8-bit integer specifying the number of times to write the byte.

#### Byte 5: byte

Unsigned 8-bit value to write to device.

#### Write String (0x24)

DEVIO, device, WRITE\_STR, string

Write the zero-terminated *string* to the device. If *string* length > 127, *string* will be truncated to 127 characters. The zero terminator is not sent unless the device is MEM, FIFO1, FIFO2, or FIFO3.

#### Bytes 4-n: string

Zero-terminated string to write to device.

#### Write from String Buffer (0x25)

DEVIO, device, WRITE SBUF

Write the contents of the string buffer to the device. A zero terminator is also sent if the device is MEM, FIFO1, FIFO2, or FIFO3.

#### Write from String Selection (0x26)

DEVIO, device, WRITE SSEL

Write the string selection to the device. A zero terminator is also sent if the device is MEM, FIFO1, FIFO2, or FIFO3.

#### Write from Memory Address 0 (0x27)

DEVIO, device, WRITE\_MEM, count

Read *count* bytes from memory, starting at memory address 0, and write the bytes to the device.

#### Byte 4: count

Unsigned 8-bit integer specifying the number of bytes to write.

#### Write from Memory Address (0x28)

DEVIO, device, WRITE\_MEMA, address, count

Read *count* bytes from memory, starting at the memory address specified by *address*, and write the bytes to the device.

#### Byte 4-5: address

Unsigned 16-bit integer specifying the memory address to write to.

#### Byte 6-7: count

Unsigned 16-bit integer specifying the number of bytes to write.

#### Write from Memory Address specified by Register (0x29)

DEVIO, device, WRITE\_MEMR, regAddr, regCount

Read the number of bytes specified in *regCount* from memory, starting at the memory address specified in *regAddr*, and write the bytes to the device.

#### Byte 4: regAddr

The lower 16-bits of the register specify the memory address to write to.

#### Byte 5: regCount

The lower 16-bits of the register specify the number of bytes to write.

#### Read 8-bit value to Register (0x30, 0x34, 0x38, 0x3C)

DEVIO, device, READ\_REG8{+ZE}{+SE}, register

Read an 8-bit value from the device and store in the lower 8 bits of the specified register.

The remaining bits in the register can be filled with either zero-extend or sign-extend.

#### Read 16-bit value to Register (0x31, 0x35, 0x39, 0x3D)

DEVIO, device, READ\_REG16{+MSB}{+LSB}{+ZE}}, register

Read a 16-bit value from the device and store in the lower 16 bits of the specified register.

The value can be stored with the most significant byte or least significant byte first. The remaining bits in the register can be filled with either zero-extend or sign-extend.

#### Read 32-bit value to Register (0x32, 0x36, 0x3A, 0x3E)

DEVIO, device, READ\_REG32{+MSB}{+LSB}{+SE}, register

Read a 32-bit value from the device and store in the lower 32 bits of the specified register.

The value can be stored with the most significant byte or least significant byte first. The remaining bits in the register can be filled with either zero-extend or sign-extend.

#### Read 64-bit value to Register (0x33, 0x37, 0x3B, 0x3F)

DEVIO, device, READ\_REG64{+MSB}{+LSB}{+ZE}}, register Read a 64-bit value from the device and store in specified register. The value can be stored with the most significant byte or least significant byte first. The remaining bits in the register can be filled with either zero-extend or sign-extend.

| Bit 7 6 5 4 | 1 3 2 1 0<br>S L Bits |           |                              |

|-------------|-----------------------|-----------|------------------------------|

|             | O L DIG               |           |                              |

| Bit 3       | Sign Extend           |           |                              |

|             | IDE Symbol            | IDE Value | Description                  |

|             | ZE                    | 0x00      | Zero extend.                 |

|             | SE                    | 0x08      | Sign extend.                 |

| Bit 2       | Byte Order            |           |                              |

|             | IDE Symbol            | IDE Value | Description                  |

|             | MSB                   | 0x00      | Most significant byte first  |

|             | LSB                   | 0x04      | Least significant byte first |

| Bits 1:0    | Number of Bits        | S         |                              |

|             | IDE Symbol            | IDE Value | Description                  |

|             | READ_REG8             | 0x30      | 1 byte (8-bit)               |

|             | READ_REG16            | 0x31      | 2 bytes (16-bit)             |

|             | READ_REG32            | 0x32      | 3 bytes (32-bit)             |

|             | READ_REG64            | 0x33      | 4 bytes (64-bit)             |

#### Byte 4: register

Register number (0 to 255).

#### Read and Skip Bytes (0x43)

DEVIO, device, READ SKIP, count

Read and skip *count* bytes from device.

Byte 4: count

Unsigned 8-bit integer specifying the number of bytes to skip.

#### Read String to String Buffer (0x45)

DEVIO, device, READ SBUF

Read zero-terminated string from device and store in string buffer.

#### Read String to String Selection (0x46)

DEVIO, device, READ\_SSEL

Read zero-terminated string from device and store at string selection point.

#### Read to Memory Address 0 (0x47)

DEVIO, device, READ\_MEM, count

Read *count* bytes from the device and store in memory, starting at memory address 0.

Byte 4: count

Unsigned byte specifying the number of bytes to read.

#### Read to Memory Address (0x48)

DEVIO, device, READ\_MEMA, address, count

Read *count* bytes from the device and store in memory, starting at the memory address specified by *address*.

Byte 4-5: address

Unsigned 16-bit integer specifying the memory address to read from.

Byte 6-7: count

Unsigned 16-bit integer specifying the number of bytes to read.

#### Read to Memory Address specified by Register (0x49)

DEVIO, device, READ\_MEMR, regAddr, regCount

Read the number of bytes specified in *regCount* from the device and store in memory starting at the memory address specified in *regAddr*.

Byte 4: regAddr

The lower 16-bits of the register specify the memory address to read from.

Byte 5: regCount

The lower 16-bits of the register specify the number of bytes to read.

# Load Device (0x5x)

DEVIO, device, LOAD\_DEVICE, xopdev

Attach the loadable *device* to the device code loaded in the XOP area of Flash memory as specified by *xopdev*. Ram is allocated from the dynamic allocation for use by the *device*. This call is required before using a loadable device.

# DEVIO, ASYNC Asynchronous Serial Port Interface

#### Syntax: DEVIO, ASYNC, action {,...}

Description:

This instruction provides support for sending and receiving data through an asynchronous serial connection. The serial connection can be configured as receive only (1 pin), transmit only (1 pin), receive and transmit (2 pins), or receive and transmit with hardware flow control (4 pins). The baud rate is selectable from 300 baud to 115,200 baud.

```

DEVIO, ASYNC, DISABLE DEVIO, ASYNC, ENABLE, pin, config

```

Opcode: DA

Byte 2: ASYNC (0x40)

#### Byte 3: action

An unsigned byte specifying the device action. Actions that are specific to the asynchronous serial device are shown below. For actions that are common to all devices, see the *DEVIO* description.

### Disable (0x00)

DEVIO, ASYNC, DISABLE

Disable the asynchronous serial connection and release the digital pins.

#### Enable (0x01)

```

DEVIO, ASYNC, ENABLE, pin, config

```

Select the pins to use for the asynchronous serial connection, set the baud rate, and enable the asynchronous serial port.

#### Byte 4: pin

Specifies the pins used for the asynchronous serial connection.

D0 to D8 28-pin uM-FPU64 chip D0 to D18 44-pin uM-FPU64 chip

#### **Pin Assignments**

```

Receive only

Rx

pin

Transmit only

Tx

pin

Receive and Transmit

Rx

pin

pin+1

Tx

Receive and Transmit with Flow Control

pin

Rx

pin+1

Tx

pin+2

/CTS

/RTS

pin+3

```

#### Byte 5: config

```

Bit 7 6 5 4 3 2 1 0

- Type Baud Rate

```

Bits 5:4 Connection Type

|         | IDE Symbol<br>RX<br>TX<br>RX_TX | IDE Value<br>0x00<br>0x10<br>0x20 | Description Receive Only Transmit Only Receive and Transmit |

|---------|---------------------------------|-----------------------------------|-------------------------------------------------------------|

|         | RX_TX_HW                        | 0x30                              | Receive and Transmit with Hardware Flow Control             |

| Bit 3:0 | <b>Baud Rate</b>                |                                   |                                                             |

|         | IDE Symbol                      | IDE Value                         | Description                                                 |

|         | -                               | -                                 | 57,600 baud                                                 |

|         | BAUD_300                        | 0x01                              | 300 baud                                                    |

|         | BAUD_600                        | 0x02                              | 600 baud                                                    |

|         | BAUD_1200                       | 0x03                              | 1200 baud                                                   |

|         | BAUD_2400                       | 0x04                              | 2400 baud                                                   |

|         | BAUD_4800                       | 0x05                              | 4800 baud                                                   |

|         | BAUD_9600                       | 0x06                              | 9600 baud                                                   |

|         | BAUD_19200                      | 0x07                              | 19200 baud                                                  |

|         | BAUD_38400                      | 80x0                              | 38400 baud                                                  |

|         | BAUD_57600                      | 0x09                              | 57600 baud                                                  |

|         | BAUD_115200                     | 0x0A                              | 115200 baud                                                 |

See Also: SERIN, SEROUT

# DEVIO, COUNTER 32-bit Counter Interface

Syntax: DEVIO, COUNTER+n, action{,...}

Description:

This instruction provides support for detecting and counting digital input changes. Optional support is provided for switch debouncing and automatic repeat when the input is held in the active state. If the active state is high, a rising edge on the digital input is counted. If the active state is low, a falling edge on the digital input is counted. If debouncing is enabled, changes to the digital input will be ignored for the *period* specified. The debounce period is set to 10 milliseconds by default. If a repeat value is specified, and the signal is held in the active state for the specified *delay*, the counter will increment at the specified *rate* while the signal remains in the active state.

```

DEVIO, COUNTER+n, DISABLE

DEVIO, COUNTER+n, ENABLE, pin, config

DEVIO, COUNTER+n, DEBOUNCE, period

DEVIO, COUNTER+n, REPEAT, delay, rate

DEVIO, COUNTER+n, READ_COUNT

DEVIO, COUNTER+n, EDGE1_MSEC

DEVIO, COUNTER+n, EDGE1_USEC

DEVIO, COUNTER+n, EDGE2_MSEC

DEVIO, COUNTER+n, EDGE2_USEC

```

Opcode: DA

Byte 2: COUNTER+n (0x50-0x53)

#### Byte 3: action

An unsigned byte specifying the device action. Actions that are specific to counter devices are shown below. For actions that are common to all devices, see the *DEVIO* description.

#### Disable (0x00)

DEVIO, COUNTER+n, DISABLE

Disable the counter and release the digital pin.

#### Enable (0x01)

DEVIO, COUNTER+n, ENABLE, pin, config

Selects the pin to use for the counter, the active level for counting, whether an event is associated with the counter, and enable the counter input.

#### Byte 4: pin

Specifies the pin to use for the counter input.

D0 to D8 28-pin uM-FPU64 chip D0 to D8 44-pin uM-FPU64 chip

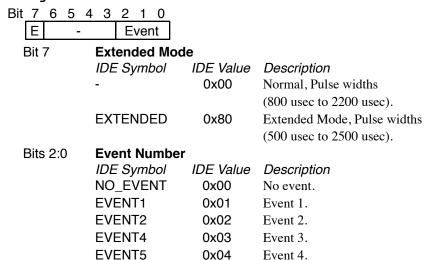

#### Byte 5: config

| Bit 7 6 5 | 4 3 2 1 0           |           |              |

|-----------|---------------------|-----------|--------------|

| Α -       | Event               |           |              |

| Bit 7     | <b>Active State</b> |           |              |

|           | IDE Symbol          | IDE Value | Description  |

|           | LOW                 | 0x00      | Active low.  |

|           | HIGH                | 0x80      | Active high. |

| Bits 2:0  | <b>Event Number</b> | •         |              |

|           | IDE Symbol          | IDE Value | Description  |

|           | NO_EVENT            | 0x00      | No event.    |

|           | EVENT1              | 0x01      | Event 1.     |

|           | EVENT2              | 0x02      | Event 2.     |

|           | EVENT4              | 0x03      | Event 3.     |

|           | EVENT5              | 0x04      | Event 4.     |

|           | EVENT6              | 0x05      | Event 5.     |

|           | EVENT7              | 0x06      | Event 6.     |

|           | EVENT1              | 0x07      | Event 7.     |

|           |                     |           |              |

#### **Set Debounce Period (0x02)**

DEVIO, COUNTER+n, DEBOUNCE, period

Specifies the debounce period in milliseconds. The counters are initialized with a debounce period of 10 milliseconds.

## Byte 4-5: **period** (unsigned word)

Specifies the debounce period in milliseconds (0 to 32677). Transitions on the counter input are ignored during the debounce period.

#### Set Repeat Rate (0x03)

DEVIO, COUNTER+n, REPEAT, delay, rate

Specifies the automatic repeat parameters. The counters are initialized with no automatic repeat.

#### Byte 4-5: **delay** (unsigned word)

Specifies the delay in milliseconds before automatic repeat is enabled. (0 to 32677)

#### Byte 6-7: rate (unsigned word)

Specifies the rate in milliseconds that the counter will be incremented if the counter input remains active. (1 to 32677)

#### Read Count (0x04)

```

DEVIO, COUNTER+n, READ_COUNT

Returns the counter value in register 0.

```

#### Read Active Edge time in milliseconds (0x05)

```

DEVIO, COUNTER+n, EDGE1_MSEC

Returns the time in milliseconds (32-bit value) in register 0 or 128.

```

### Read Active Edge time in microseconds (0x06)

```

DEVIO, COUNTER+n, EDGE1_USEC

Returns the time in microseconds (64-bit value) in register 0 or 128.

```

### Read Not Active Edge time in milliseconds (0x07)

```

DEVIO, COUNTER+n, EDGE2_MSEC

Returns the time in milliseconds (32-bit value) in register 0 or 128.

```

## Read Not Active Edge time in microseconds (0x08)

```

DEVIO, COUNTER+n, EDGE2_USEC

Returns the time in microseconds (64-bit value) in register 0 or 128.

```

# DEVIO, FIFO FIFO Buffer Interface

```

Syntax: DEVIO,FIFO1,action{,...}

DEVIO,FIFO2,action{,...}

DEVIO,FIFO3,action{,...}

DEVIO,FIFO4,action{,...}

```

Description:

These instructions provide support for First In First Out (FIFO) buffers. They can be used to buffer data, or to transfer data from one process to another. Memory must be allocated to the FIFOs from the dynamic allocation area using one of the following instructions:

```

DEVIO, MEM, ALLOCATE, memSize, fifoSize

DEVIO, FIFOn, ALLOC_MEM, size

DEVIO, FIFOn, ALLOC_MEMR, regSize

DEVIO, FIFOn, DISABLE

DEVIO, FIFOn, ENABLE, pin, config

DEVIO, FIFOn, CLEAR

DEVIO, FIFOn, USED

DEVIO, FIFOn, FREE

DEVIO, FIFOn, STATUS

DEVIO, FIFOn, CLEAR_OVERFLOW

DEVIO, FIFOn, ALLOC_MEM, size

DEVIO, FIFOn, ALLOC_MEMR, regSize

```

Opcode: DA

#### Byte 2: FIF01-FIF03 (0x01-0x04)

#### Byte 3: action

An unsigned byte specifying the device action. Actions that are specific to FIFO devices are shown below. For actions that are common to all devices, see the *DEVIO* description.

## Disable (0x00)

DEVIO, FIFOn, DISABLE Disables the specified FIFO device.

### Enable (0x01)

DEVIO, FIFOn, ENABLE, pin, config Initialize the FIFO.

#### Byte 4: pin

Unused.

#### Byte 5: config

### Clear Buffer (03)

DEVIO, FIFOn, CLEAR